Purpose:

This post shows the procedures to upgrade FPGA via ONIE on switch.

Model:

AS7712-32X

Preparation:

A. Personal computer

B. FPGA_Updater

Download the FPGA-updater image for your own device.

C. Serial Console cable:

A cable which attached in the original box.

D. Console terminal

Putty,Teraterm,SecureCRT,etc...

E. Empty USB drive or transport protocol tools

USB drive

TFTP server

FTP server

Http file server

OpenSSH

Procedure:

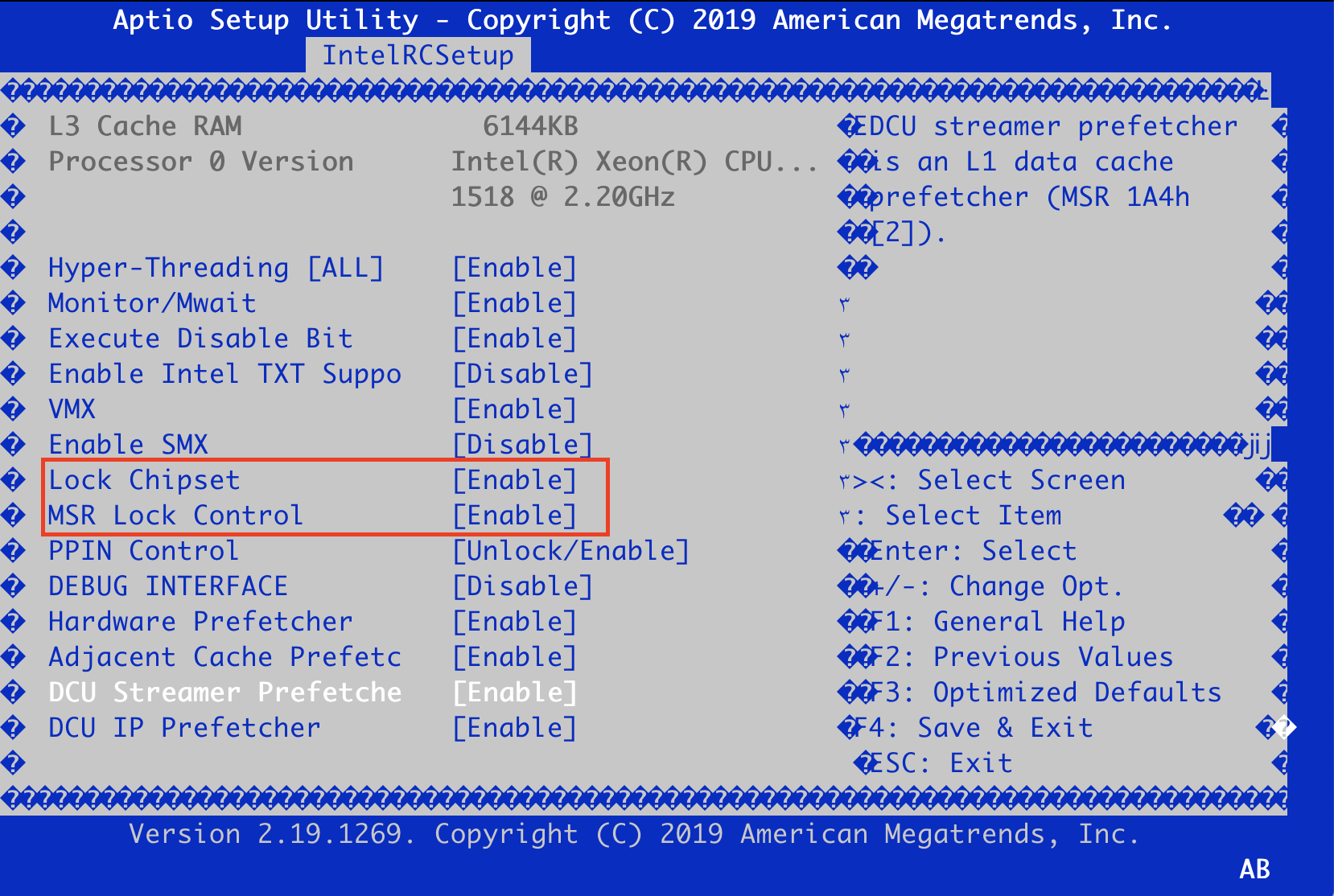

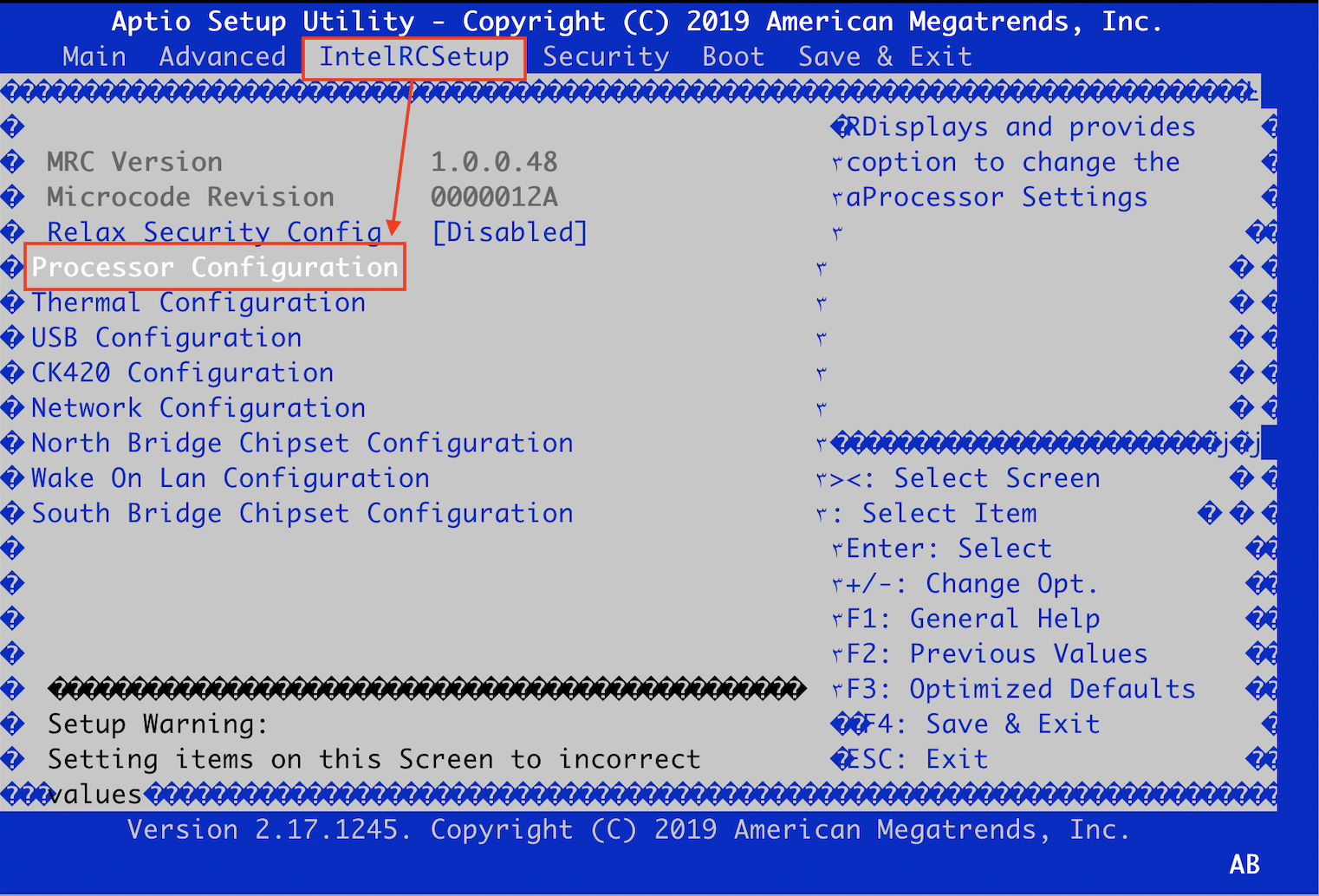

STEP1. Reboot the switch and then press "ESC" to enter the BIOS setting. (e.g., as7726_32x)

1. Check the version and then press "ESC".

Note: If your model belongs to AS5916/AS7326/AS7716/AS7726 and the current BIOS version is v36 or later, STEP1 should be processed before the upgrade, else please ignore this step.

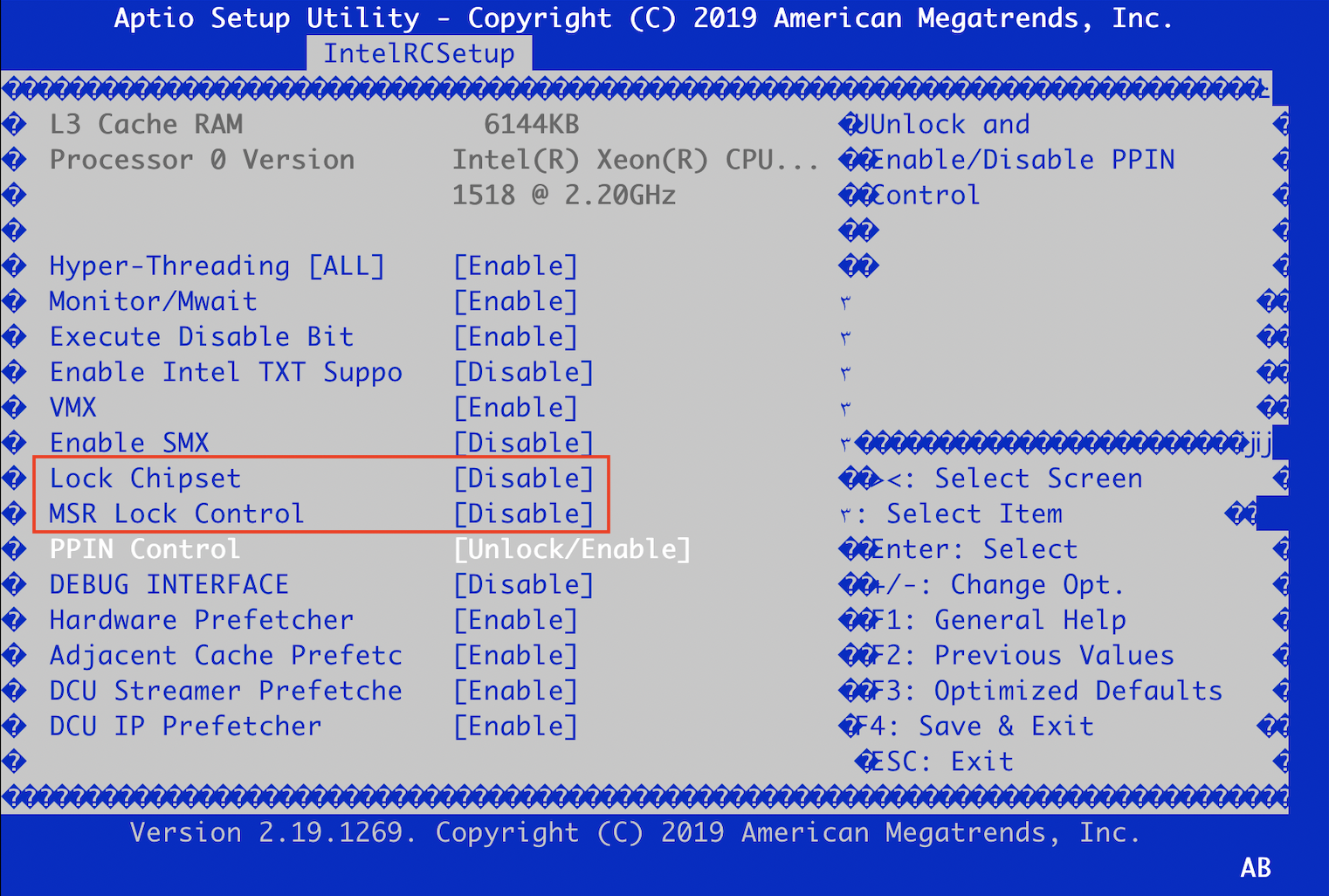

*set Lock Chipset to: Disable

*set MSR Lock Control to: Disable

2. Please follow the red marked.

3. Please disable the following red marked

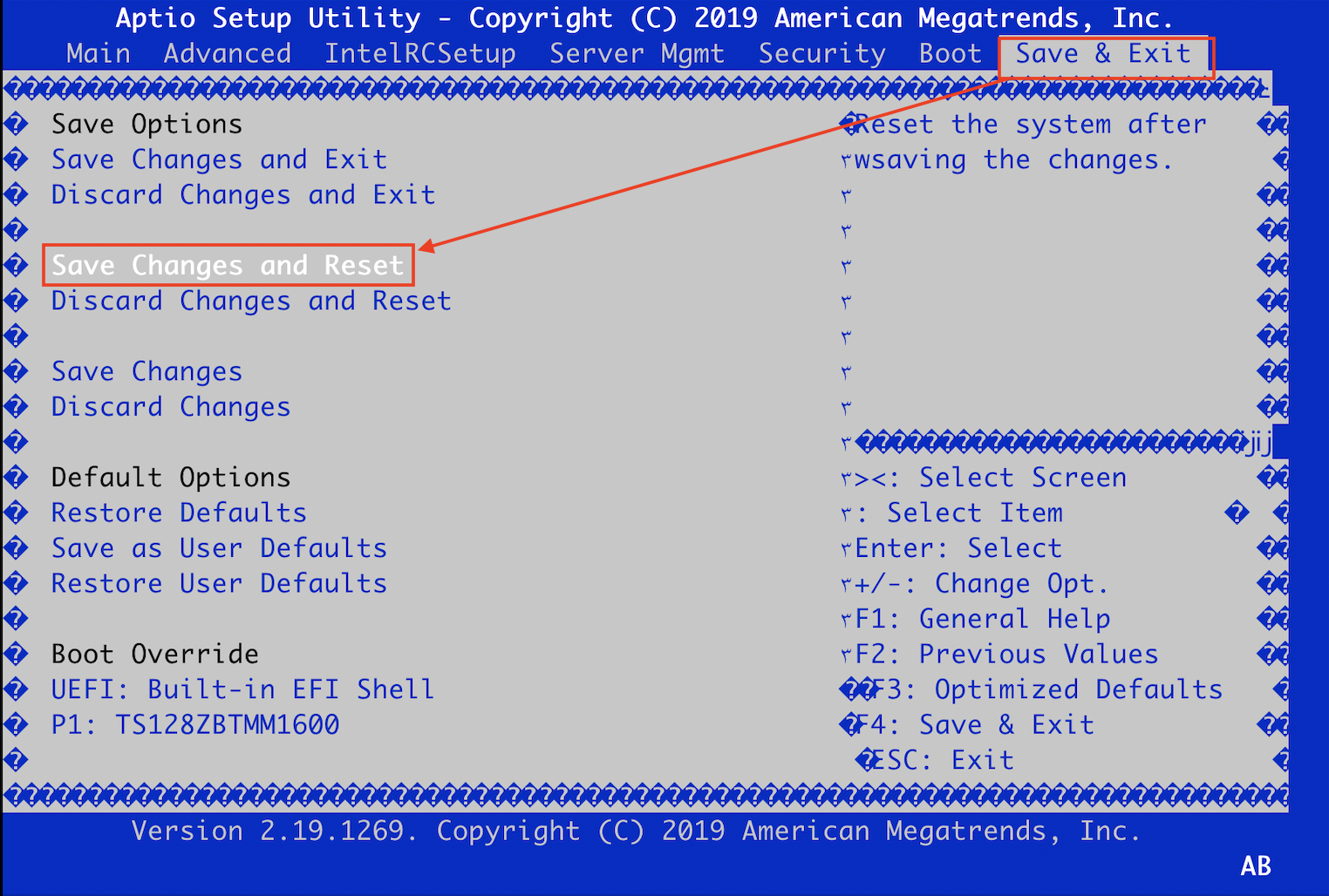

4. Save changes and reset.

STEP2. Start the upgrade process (5 examples)

USB drive

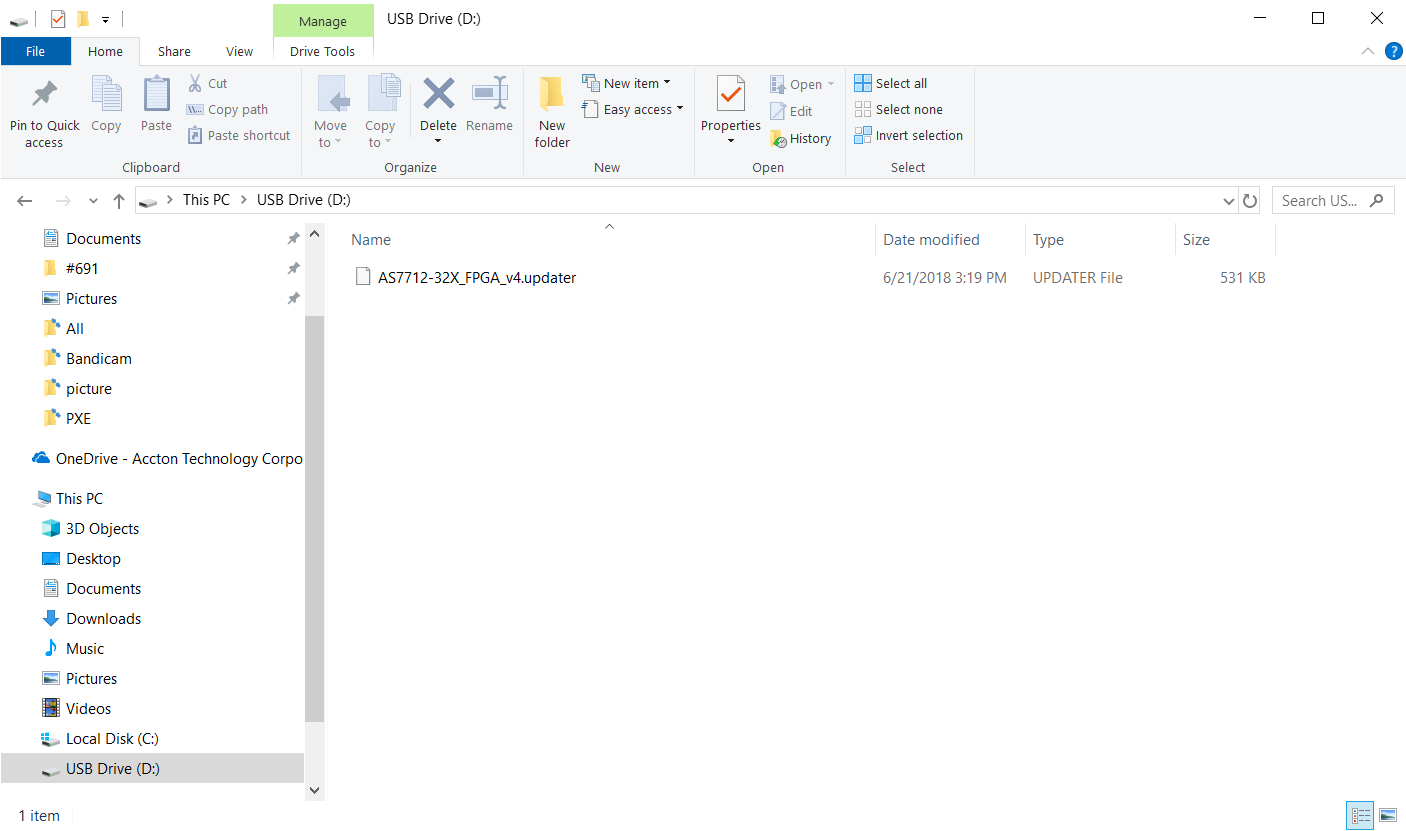

1. Put the FPGA_Updater to the USB drive. (e.g., as7712-32x)

2. Insert the USB drive into the data center front panel.

![]()

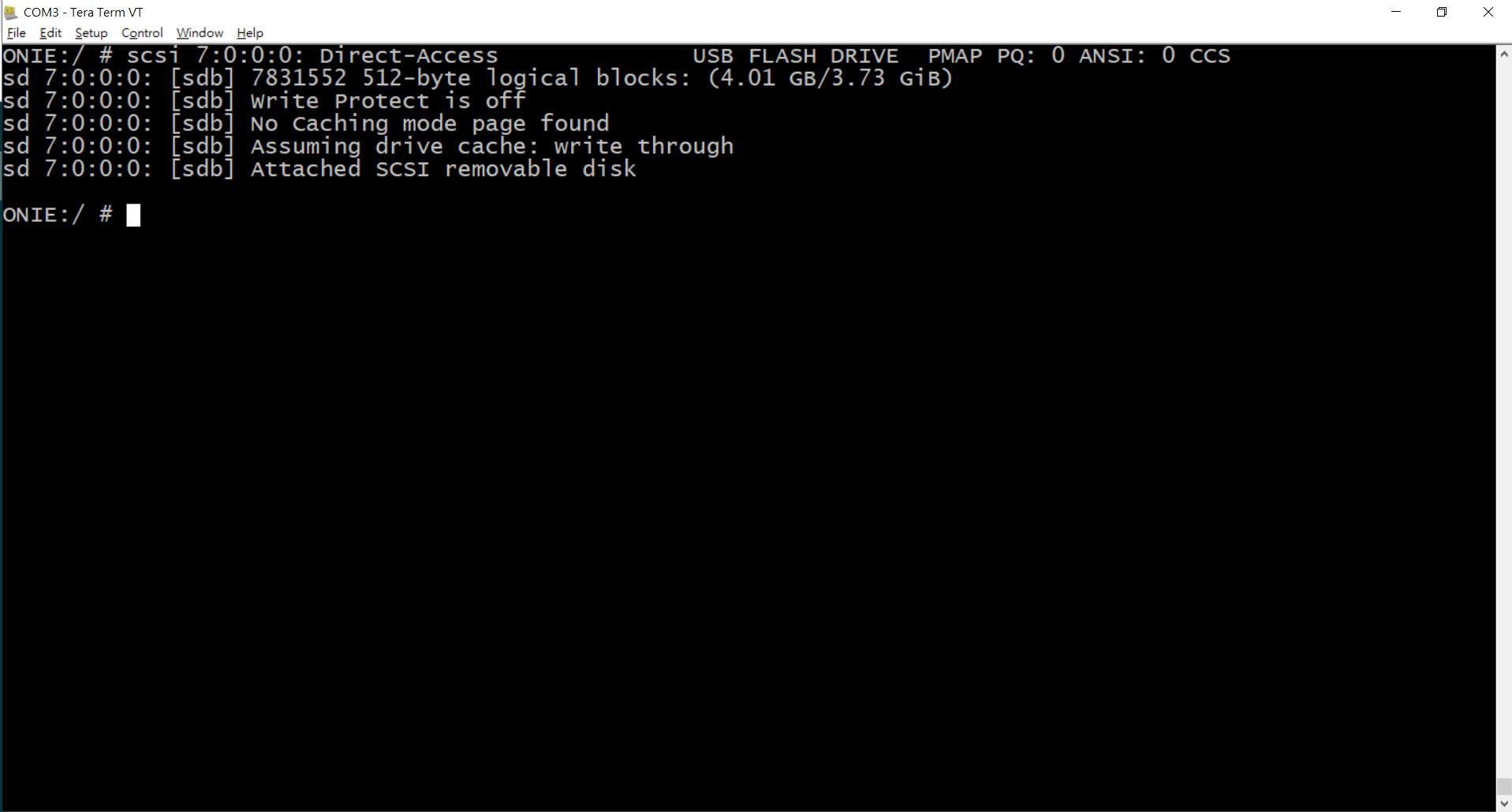

3. The terminal will show the following message.

4.Input "fdisk -l" command to show the storage status (e.g., /dev/sdb)

ONIE:/mnt/usb # Disk /dev/sda: 31.4 GB, 31488000000 bytes 255 heads, 63 sectors/track, 3828 cylinders Units = cylinders of 16065 * 512 = 8225280 bytes Device Boot Start End Blocks Id System /dev/sda1 * 1 3829 30749999+ ee EFI GPT Device Boot Start End Blocks Id System /dev/sdb1 ? 253420 474801 850989111+ 6e Unknown Partition 1 has different physical/logical beginnings (non-Linux?): phys=(97, 115, 32) logical=(253419, 0, 14) Partition 1 has different physical/logical endings: phys=(107, 121, 32) logical=(474800, 17, 54) Partition 1 does not end on cylinder boundary /dev/sdb2 ? 1 1 0 74 Unknown Partition 2 has different physical/logical beginnings (non-Linux?): phys=(370, 116, 33) logical=(0, 0, 1) Partition 2 has different physical/logical endings: phys=(0, 13, 10) logical=(558658, 74, 4) Partition 2 does not end on cylinder boundary /dev/sdb4 3649 3649 220+ 0 Empty Partition 4 has different physical/logical beginnings (non-Linux?): phys=(0, 0, 0) logical=(3648, 57, 51) Partition 4 has different physical/logical endings: phys=(0, 0, 0) logical=(3648, 64, 57) Partition 4 does not end on cylinder boundary Partition table entries are not in disk order

Note: /dev/sda is original hard drive, mSATA, 32G

5. Mount the USB drive and check the mount status.

ONIE:/mnt # ONIE:/mnt # ONIE:/mnt # /dev/sdb on /mnt/usb type vfat (rw,relatime,fmask=0022,dmask=0022,codep age=437,iocharset=iso8859-1,shortname=mixed,errors=re

6. Copy the FPGA_Updater to local storage. (e.g., /tmp)

ONIE:/mnt/usb # ls AS7712-32X_FPGA_v4.updater System Volume Information ONIE:/mnt/usb # cp AS7712-32X_FPGA_v4.updater /tmp

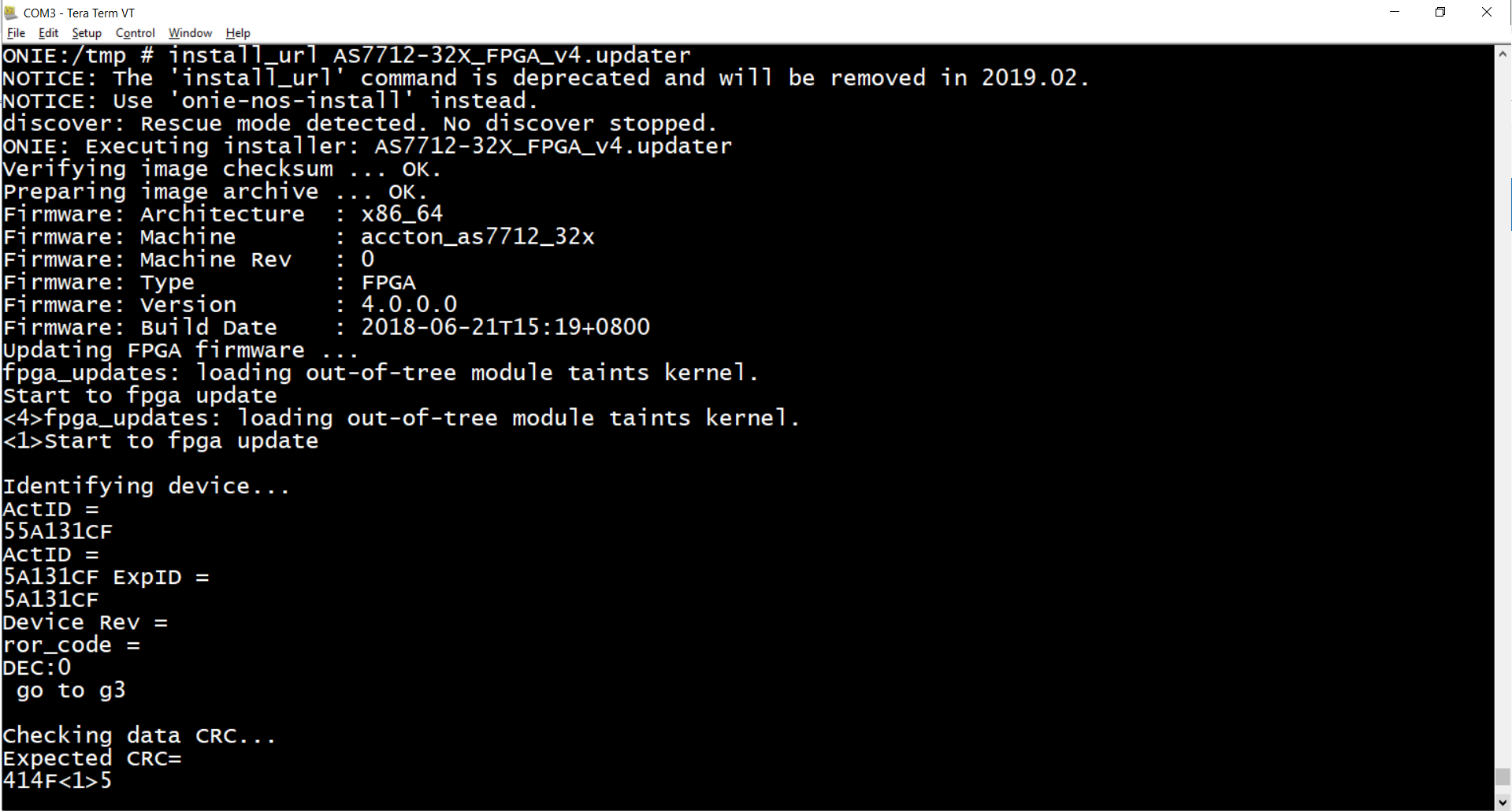

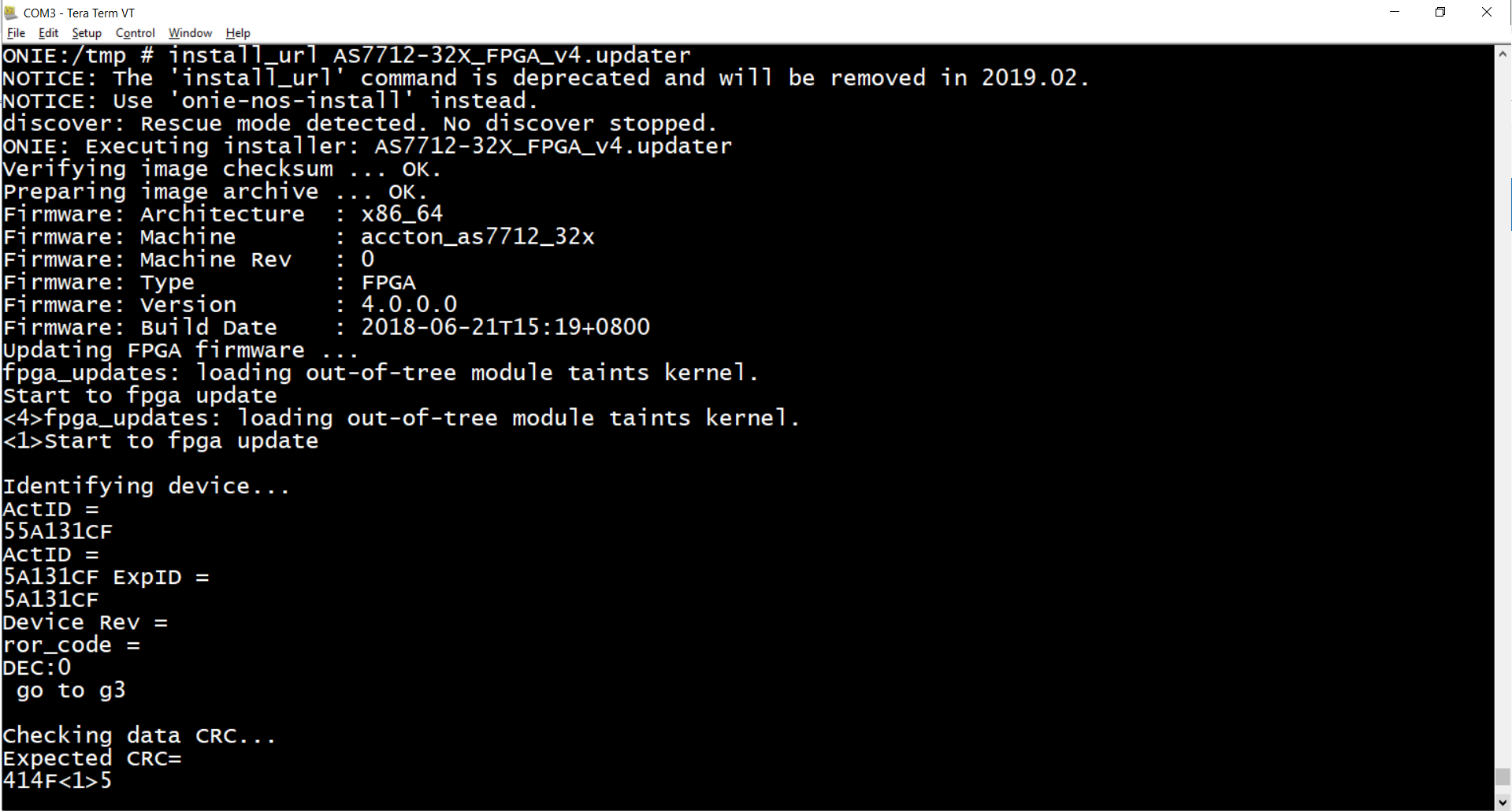

7. Upgrade the FPGA by "install_url [FGPA_Updater]" command.

ONIE:/ # ONIE:/tmp # AS7712-32X_FPGA_v4.updater ONIE:/tmp #

8. FPGA will be upgraded immediately.

TFTP

1. Please connect to the TFTP server with Mgmt port. (e.g., AS7716-32x)

Note: Please use 1G port.

![]()

2. Set the IP address in ONIE and try to ping the TFTP server. (Server IP: 192.168.0.200)

ONIE:/ # ONIE:/ # eth0 Link encap:Ethernet HWaddr CC:37:AB:C4:B1:0C inet6 addr: fe80::ce37:abff:fec4:b10c/64 Scope:Link UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1 RX packets:77 errors:0 dropped:0 overruns:0 frame:0 TX packets:31 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:7619 (7.4 KiB) TX bytes:7134 (6.9 KiB) Memory:dff00000-dff1ffff PING 192.168.0.200 (192.168.0.200): 56 data bytes 64 bytes from 192.168.0.200: seq=0 ttl=128 time=9.675 ms 64 bytes from 192.168.0.200: seq=1 ttl=128 time=0.517 ms ^C --- 192.168.0.200 ping statistics --- 2 packets transmitted, 2 packets received, 0% packet loss round-trip min/avg/max = 0.517/5.096/9.675 ms

3. Input "install_url [TFTP file location]" command and the upgrade will start.

ONIE:/ # install_url tftp://192.168.0.200/AS7712-32X_FPGA_v4.updater

4. FPGA will be upgraded immediately.

FTP

1. Please connect to the FTP server with Mgmt port. (e.g., AS7712-32x)

Note: Please use 1G port.

![]()

2. Set the IP address in ONIE and try to ping the FTP server. (Server IP: 192.168.0.200)

ONIE:/ # ONIE:/ # eth0 Link encap:Ethernet HWaddr CC:37:AB:C4:B1:0C inet6 addr: fe80::ce37:abff:fec4:b10c/64 Scope:Link UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1 RX packets:77 errors:0 dropped:0 overruns:0 frame:0 TX packets:31 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:7619 (7.4 KiB) TX bytes:7134 (6.9 KiB) Memory:dff00000-dff1ffff PING 192.168.0.200 (192.168.0.200): 56 data bytes 64 bytes from 192.168.0.200: seq=0 ttl=128 time=9.675 ms 64 bytes from 192.168.0.200: seq=1 ttl=128 time=0.517 ms ^C --- 192.168.0.200 ping statistics --- 2 packets transmitted, 2 packets received, 0% packet loss round-trip min/avg/max = 0.517/5.096/9.675 ms

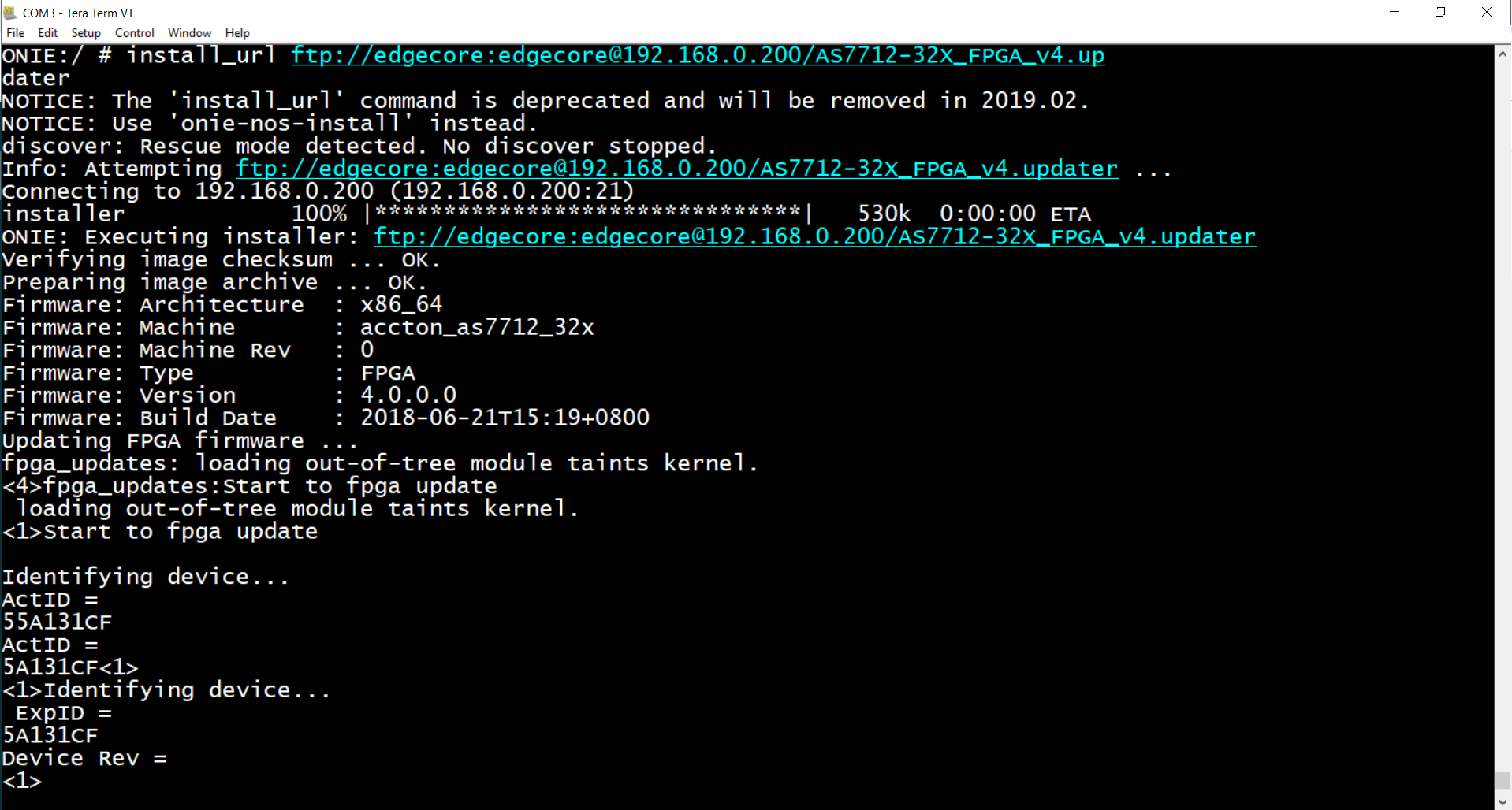

3. Input "install_url [FTP account:password@location]" command and the upgrade will

start.

ONIE:/ # install_url ftp://edgecore:edgecore@192.168.0.200/AS7712-32X_FPGA_v4.updater

4. FPGA will be upgraded immediately.

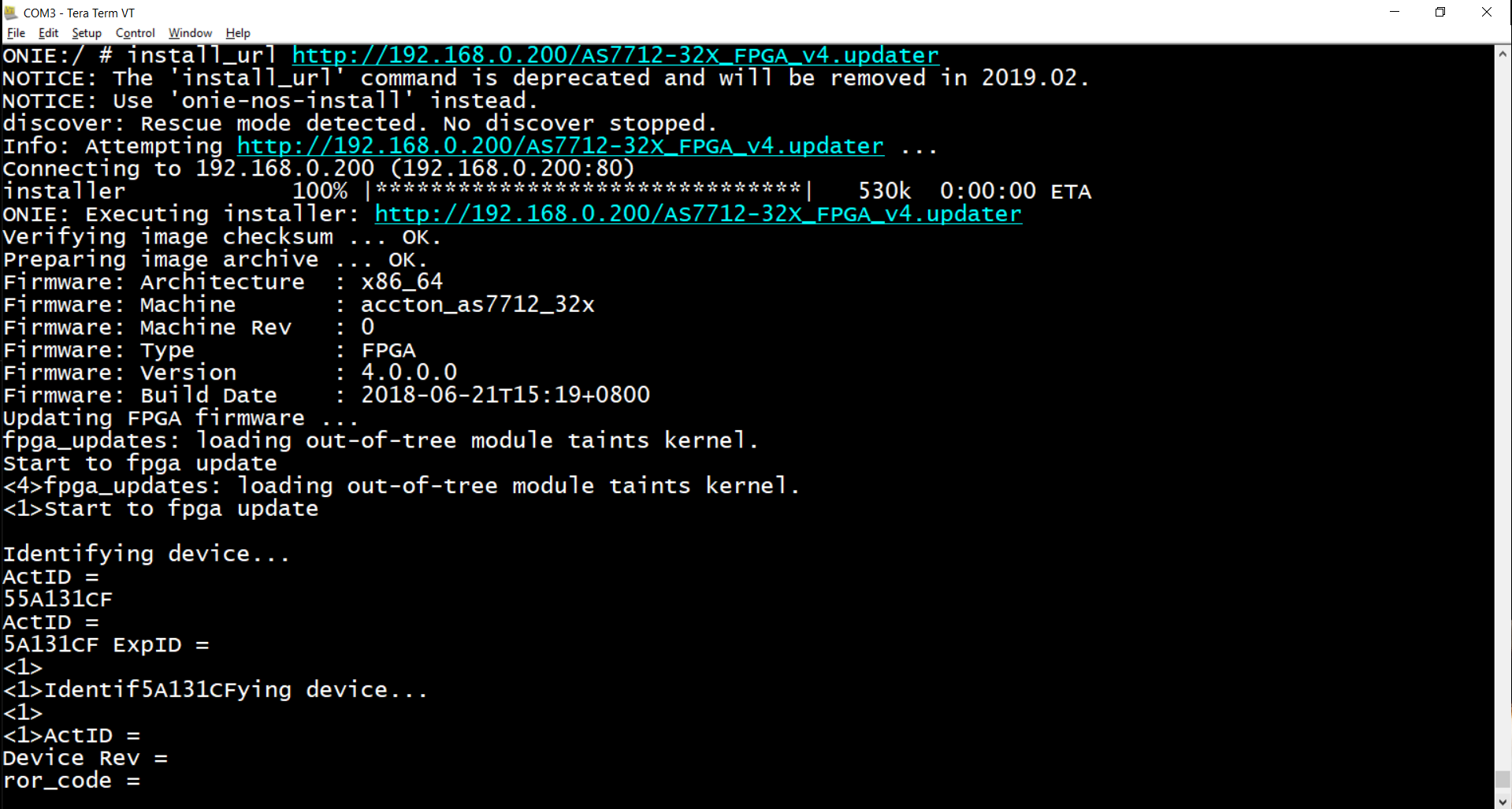

HTTP

1. Please connect to the HTTP server with Mgmt port. (e.g., AS7712-32x)

Note: Please use 1G port.

![]()

2. Set the IP address in ONIE and try to ping the HTTP server. (Server IP: 192.168.0.200)

ONIE:/ # ONIE:/ # eth0 Link encap:Ethernet HWaddr CC:37:AB:C4:B1:0C inet6 addr: fe80::ce37:abff:fec4:b10c/64 Scope:Link UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1 RX packets:77 errors:0 dropped:0 overruns:0 frame:0 TX packets:31 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:7619 (7.4 KiB) TX bytes:7134 (6.9 KiB) Memory:dff00000-dff1ffff PING 192.168.0.200 (192.168.0.200): 56 data bytes 64 bytes from 192.168.0.200: seq=0 ttl=128 time=9.675 ms 64 bytes from 192.168.0.200: seq=1 ttl=128 time=0.517 ms ^C --- 192.168.0.200 ping statistics --- 2 packets transmitted, 2 packets received, 0% packet loss round-trip min/avg/max = 0.517/5.096/9.675 ms

3. Input "install_url [HTTP URL]" command and the upgrade will start.

ONIE:/ # install_url http://192.168.0.200/AS7712-32X_FPGA_v4.updater

4. FPGA will be upgraded immediately.

SCP

1. Please connect to the OpenSSH server with Mgmt port. (e.g., AS7712-32x)

Note: Please use 1G port.

![]()

2. Set IP address in ONIE and try to ping the OpenSSH server. (Server IP: 192.168.0.100)

ONIE:/ # ONIE:/ # eth0 Link encap:Ethernet HWaddr CC:37:AB:C4:B1:0C inet6 addr: fe80::ce37:abff:fec4:b10c/64 Scope:Link UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1 RX packets:77 errors:0 dropped:0 overruns:0 frame:0 TX packets:31 errors:0 dropped:0 overruns:0 carrier:0 collisions:0 txqueuelen:1000 RX bytes:7619 (7.4 KiB) TX bytes:7134 (6.9 KiB) Memory:dff00000-dff1ffff ONIE:/ # PING 192.168.0.100 (192.168.0.100): 56 data bytes 64 bytes from 192.168.0.100: seq=0 ttl=64 time=0.705 ms 64 bytes from 192.168.0.100: seq=1 ttl=64 time=0.433 ms ^C --- 192.168.0.100 ping statistics --- 2 packets transmitted, 2 packets received, 0% packet loss round-trip min/avg/max = 0.433/0.569/0.705 ms

3. Use the "SCP" command to copy the FPGA_Updater from the SSH server.

scp [account@server ip]:[installer_file_path] [local_path]

ONIE:/ # scp jeff_cheng@192.168.0.100:/Users/jeff_cheng/Desktop/ISO/7712-32x/FPGA/AS7712-32X_FPGA_v4.updater /tmp Host '192.168.0.100' is not in the trusted hosts file. (ecdsa-sha2-nistp256 fingerprint md5 be:26:8f:8c:2f:26:69:f5:05:7e:30:d2 :d2:01:e0:92) Do you want to continue connecting? (y/n) y jeff_cheng@192.168.0.100's password: AS7712-32X_FPGA_v4.updater 100% 636KB 635.6KB/s 00:00

4. Upgrade the FPGA by "install_url [FPGA_Updater]" command.

ONIE:/ # ONIE:/tmp # AS7712-32X_FPGA_v4.updater ONIE:/tmp #

5. FPGA will be upgraded immediately.

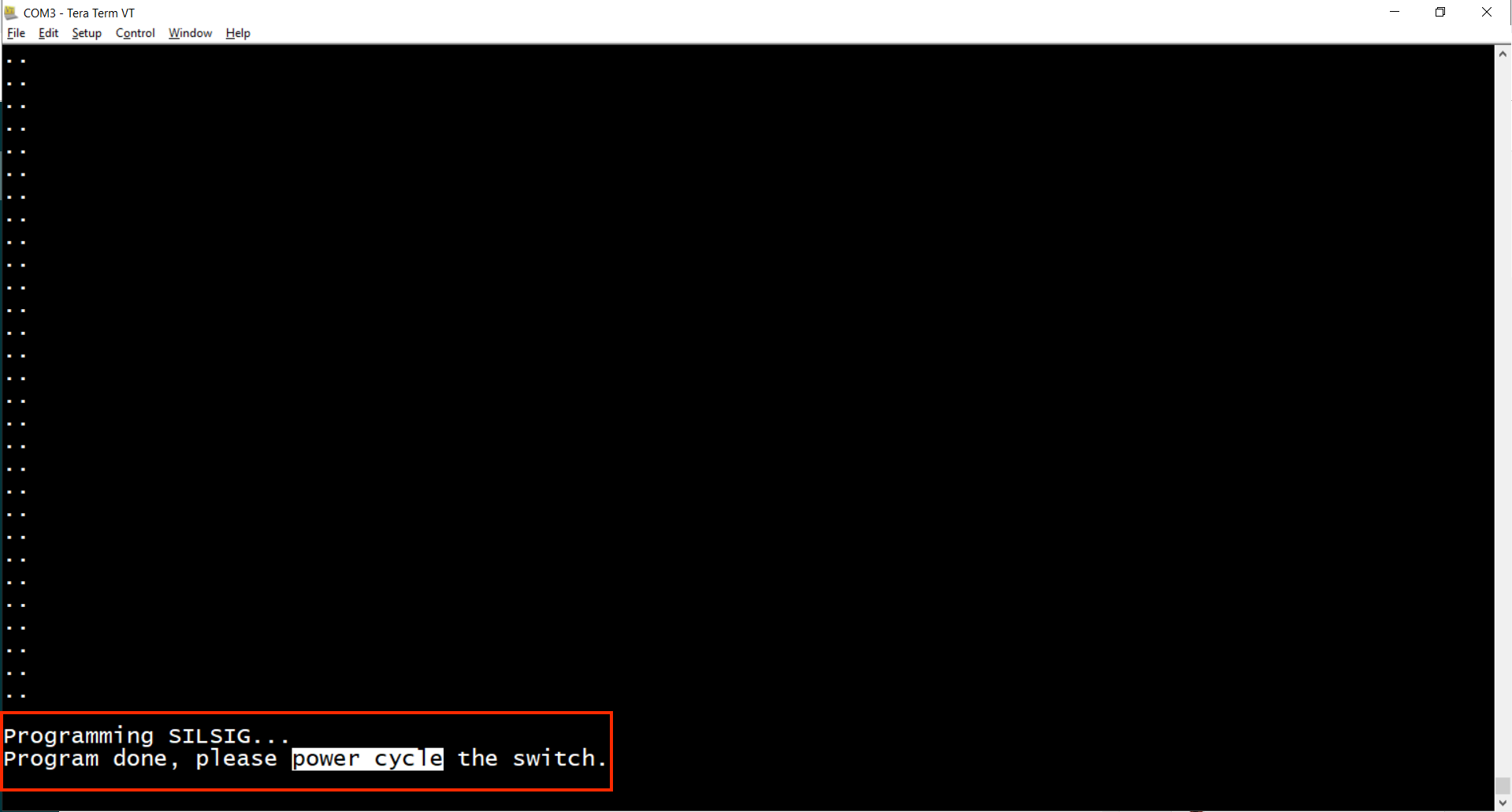

STEP3. After upgrade, you need power cycle the switch by manual.

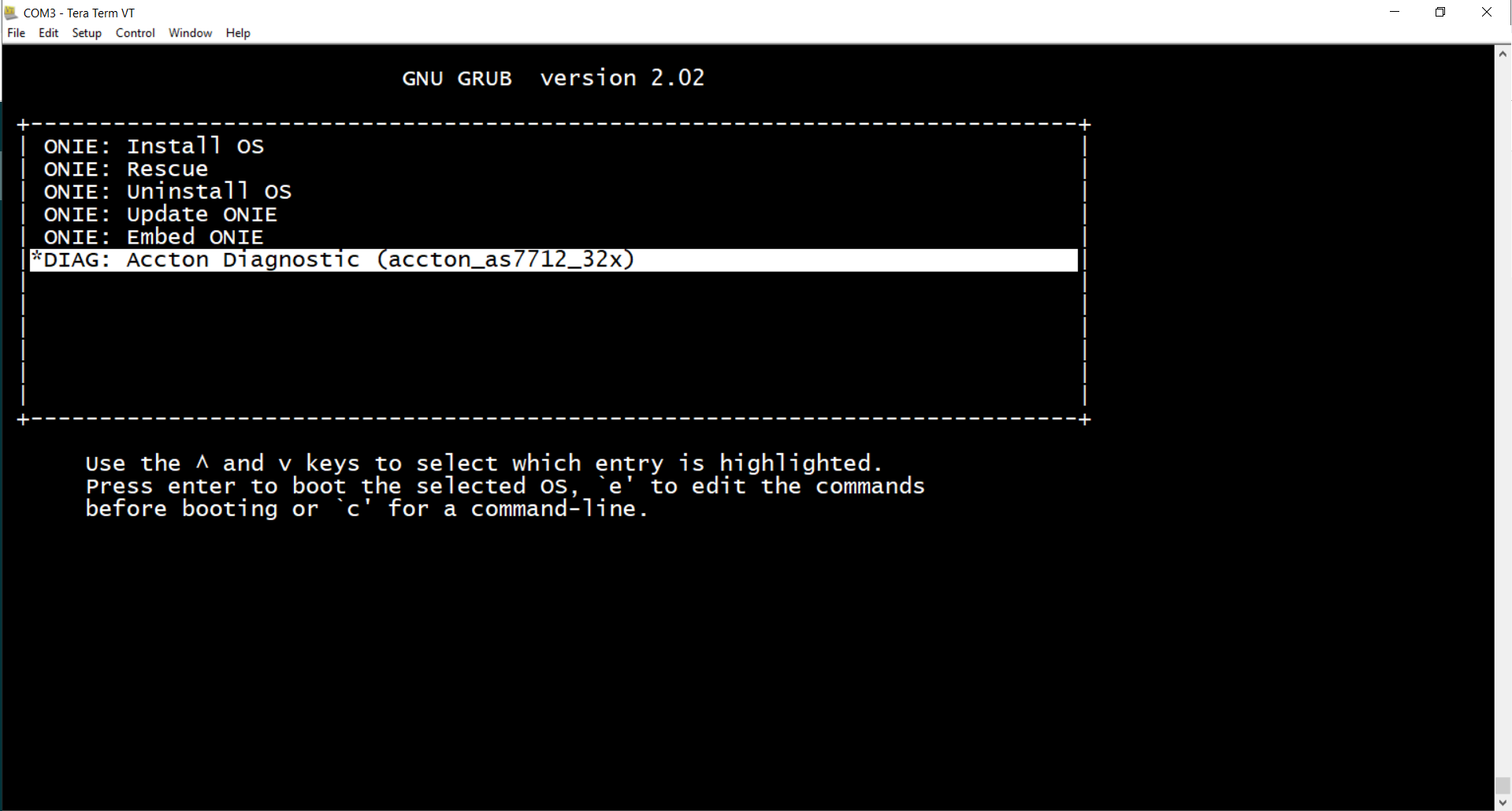

STEP4. Please enter the "Accton-diag" mode when the switch is opened.

STEP5. Check the FPGA version with "show_chip_ver".

root@(none):/# CPLD1 Ver (0x60).0x1 = 0a CPLD2 Ver (0x62).0x1 = 0b CPLD3 Ver (0x64).0x1 = 0b CPLDFAN Ver (0x66).0x1 = 08

STEP6. After the upgrade, please return to STEP3 and then "enable" the setting back.